# CENGAGE INDIA EDITION

# Avtar Singh S. Srinivasan Digital Signal Processing

Implementations Using DSP Microprocessors with Examples from TMS320C54xx

# **Digital Signal Processing Implementations**

Using DSP Microprocessors—with Examples from TMS320C54xx

Avtar Singh San Jose State University

S. Srinivasan Indian Institute of Technology, Madras

Andover • Melbourne • Mexico City • Stamford, CT • Toronto • Hong Kong • New Delhi • Seoul • Singapore • Tokyo

Digital Signal Processing Implementations Avtar Singh & S. Srivnivasan

© 2004 by Brooks/Cole, a part of Cengage Learning

This edition is reprinted with license from Brooks/Cole, a part of Cengage Learning, for sale in India, Pakistan, Bangladesh, Nepal and Sri Lanka.

ALL RIGHTS RESERVED. No part of this work covered by the copyright herein may be reproduced, transmitted, stored or used in any form or by any means graphic, electronic, or mechanical, including but not limited to photocopying, recording, scanning, digitizing, taping, Web distribution, information networks, or information storage and retrieval systems, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without the prior written permission of the publisher

ISBN-13: 978-81-315-0034-7 ISBN-10: 81-315-0034-9

Cengage Learning India Private Limited 418, F.I.E., Patparganj Delhi 110092 India

Tel: 91-11-43641111 Fax: 91-11-43641100 Email: asia.infoindia@cengage.com

Cengage Learning is a leading provider of customized learning solutions with office locations around the globe, including Andover, Melbourne, Mexico City, Stamford (CT), Toronto, Hong Kong, New Delhi, Seoul, Singapore, and Tokyo. Locate your local office at: www.cengage.com/global

Cengage Learning Products are represented in Canada by Nelson Education, Ltd.

For product information, visit our website at www.cengage.co.in

Printed in India Eleventh Indian Reprint 2011

# Contents

# Chapter 1

|     | Introduction                                             | •   |

|-----|----------------------------------------------------------|-----|

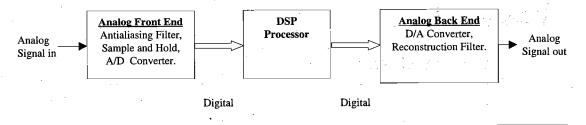

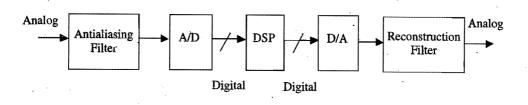

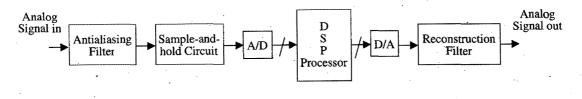

| 1.1 | A Digital Signal-Processing System                       |     |

| 1.2 | Programmable Digital Signal Processors                   | . 2 |

| 1.3 | Major Features of Programmable Digital Signal Processors | 3   |

| 1.4 | The Scope of the Book                                    | 4   |

|     | References                                               | 1   |

|     | Introduction to Digital Signal Processing          | •           | •       | 6   |

|-----|----------------------------------------------------|-------------|---------|-----|

| 2.1 | Introduction                                       |             |         | 6   |

| 2.2 | A Digital Signal-Processing System                 |             | · · · · | . 6 |

| 2.3 | The Sampling Process                               |             |         | 7   |

| 2.4 | Discrete Time Sequences                            |             |         | 9   |

| 2.5 | Discrete Fourier Transform (DFT) and Fast Fourie   | r Transform | (FFT)   | 10  |

|     | 2.5.1 The DFT Pair 10                              |             |         |     |

|     | 2.5.2 The Relationship between DFT and Frequency F | tesponse 11 |         |     |

|     | 2.5.3 The Fast Fourier Transform (FFT) 11          |             |         |     |

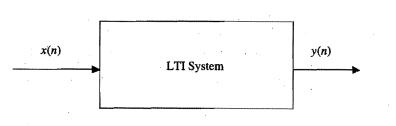

| 2,6 | Linear Time-Invariant Systems                      |             |         | 12  |

|     | 2.6.1 Convolution 13                               |             |         |     |

| •   | 2.6.2 Z-Transform 13                               |             |         |     |

|     | 2.6.3 The System Function 13                       |             |         |     |

| 2.7 | Digital Filters                                    | -           | •       | 14  |

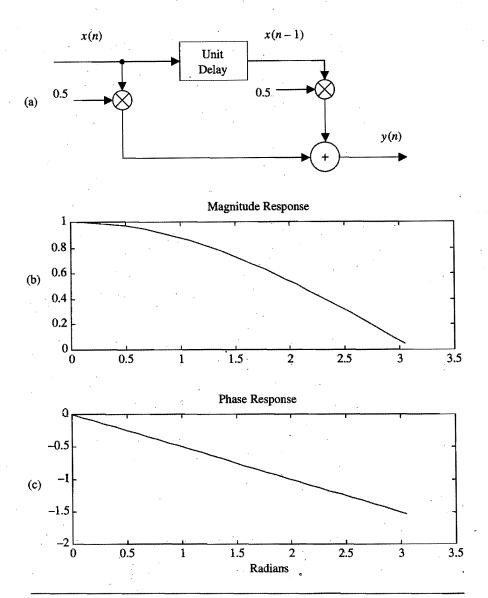

|     | 2.7.1 Finite Impulse Response (FIR) Filters 14     | 5 a         | •       |     |

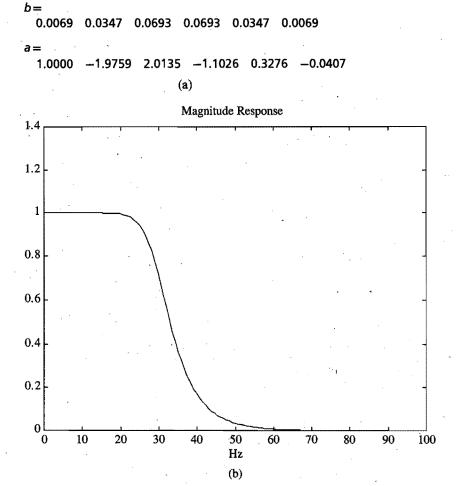

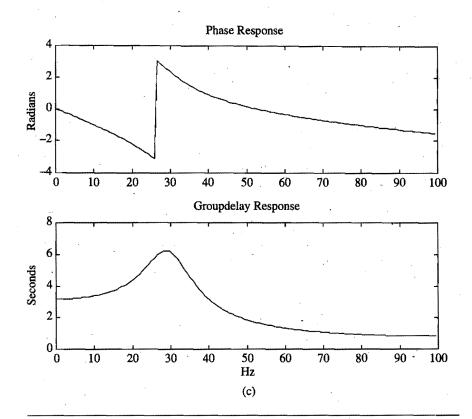

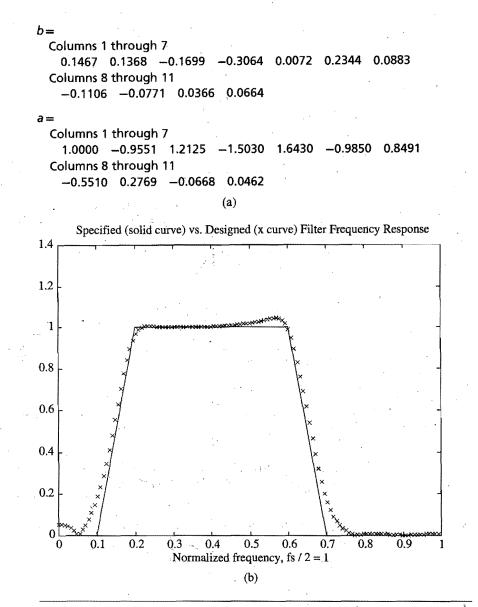

|     | 2.7.2 Infinite Impulse Response (IIR) Filters 17   |             |         | * ' |

|     | 2.7.3 FIR Filter Design 19                         | •           | *       |     |

|     | 2.7.4 IIR Filter Design 20                         |             |         |     |

|     | ·                                                  | •           |         | 111 |

|     |                                                    |             |         |     |

| iv. | Contents |

|-----|----------|

|     |          |

|      | 2.8<br>2.9<br>2.10 | Decimation and Interpolation<br>Analysis and Design Tool for DSP Systems: MATLAB<br>Digital Signal Processing Using MATLAB                                                                  | 21<br>23<br>24<br>38 |

|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|      | 2.11               | Summary<br>References                                                                                                                                                                       | 38                   |

|      | e                  | References -                                                                                                                                                                                | 38                   |

|      |                    | Assignments<br>Laboratory Assignment                                                                                                                                                        | -36<br>-40           |

|      |                    | Laboratory Assignment                                                                                                                                                                       | 40                   |

| Cha  | pter               | 3                                                                                                                                                                                           |                      |

| Criu | peer               | Computational Accuracy in DSP Implementations                                                                                                                                               | 42                   |

|      | 3.1                | Introduction                                                                                                                                                                                | 47                   |

|      | 3.1<br>3.2         |                                                                                                                                                                                             | 42                   |

| · .  | 5.2                | Number Formats for Signals and Coefficients in DSP Systems                                                                                                                                  | 42                   |

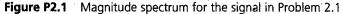

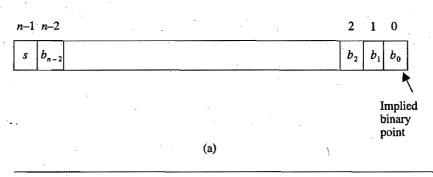

|      |                    | <ul> <li>3.2.1 Fixed-Point Format 43</li> <li>3.2.2 Double-Precision Fixed-Point Format 44</li> <li>3.2.3 Floating-Point Format 44</li> <li>3.2.4 Block Floating-Point Format 46</li> </ul> |                      |

|      | 3.3                | Dynamic Range and Precision                                                                                                                                                                 | 47                   |

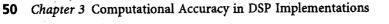

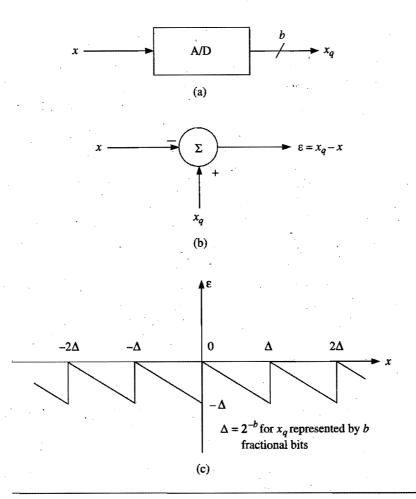

|      | 3.4                | Sources of Error in DSP Implementations                                                                                                                                                     | 19                   |

|      | 3.5                | A/D Conversion Errors                                                                                                                                                                       | 49                   |

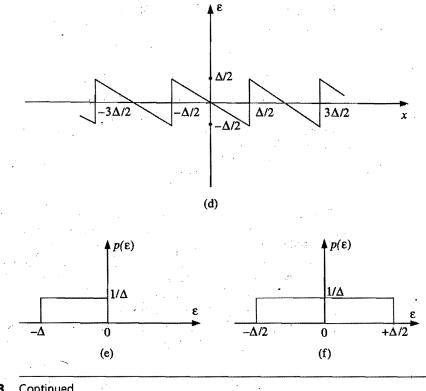

|      | 3.6                | DSP Computational Errors                                                                                                                                                                    | 52                   |

|      | 3.7                | D/A Conversion Errors                                                                                                                                                                       | 54                   |

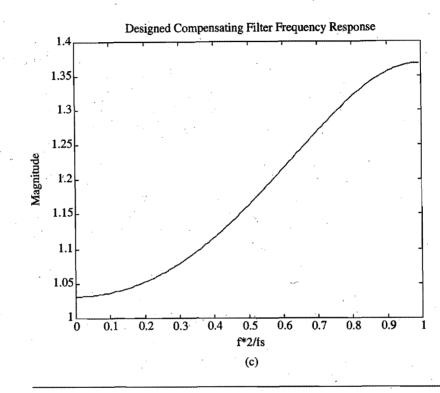

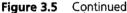

|      |                    | 3.7.1 Compensating Filter 57                                                                                                                                                                |                      |

|      | 3.8                | Summary                                                                                                                                                                                     | 59                   |

| 2    |                    | References                                                                                                                                                                                  | 59                   |

|      |                    | Assignments                                                                                                                                                                                 | 59                   |

|      |                    |                                                                                                                                                                                             |                      |

|      |                    |                                                                                                                                                                                             |                      |

| Cha  | pter               | 4                                                                                                                                                                                           |                      |

| . •  |                    | Architectures for Programmable Digital<br>Signal-Processing Devices                                                                                                                         | 61                   |

| :.+  | 4.1                | Introduction                                                                                                                                                                                | 61                   |

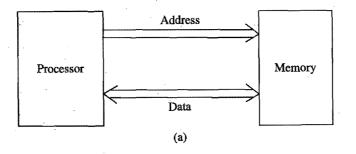

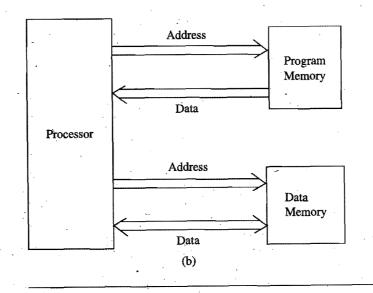

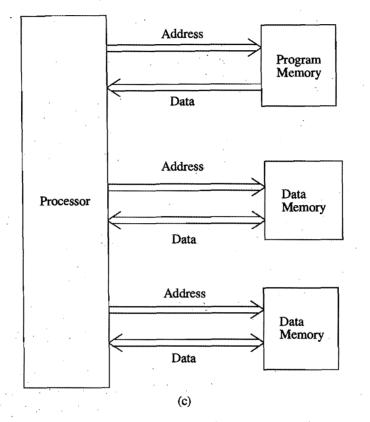

|      | 4.2                | Basic Architectural Features                                                                                                                                                                | 61                   |

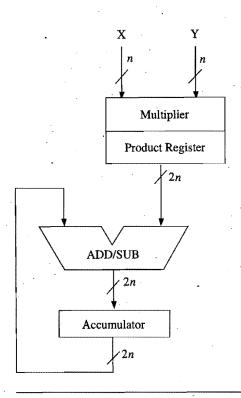

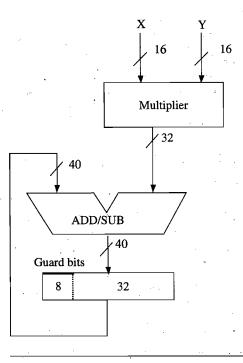

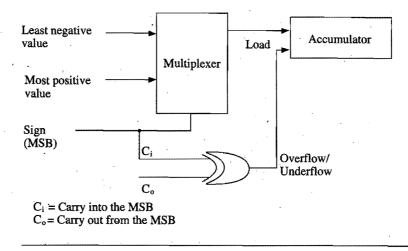

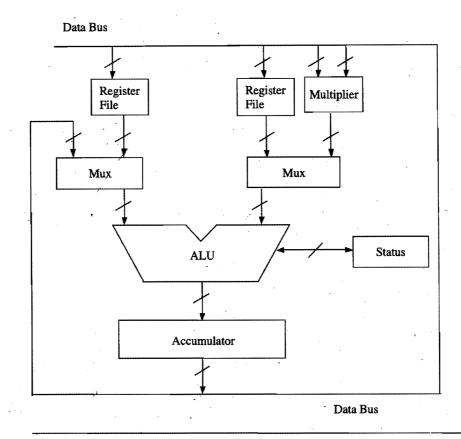

|      | 4.3                | DSP Computational Building Blocks                                                                                                                                                           | 63                   |

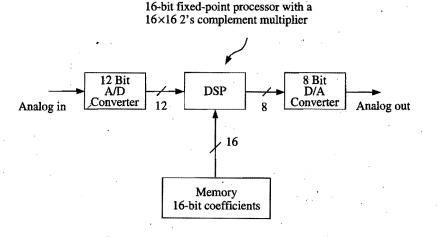

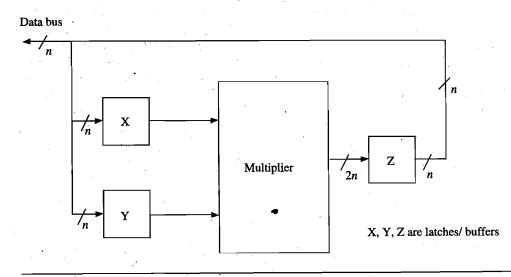

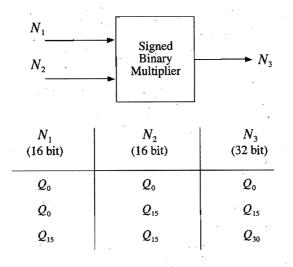

4.3.1 Multiplier 63

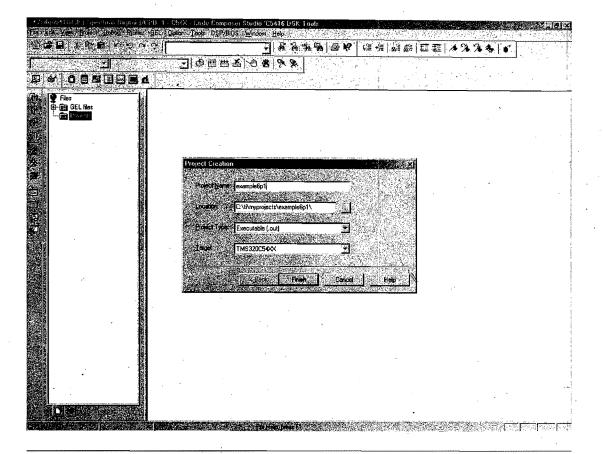

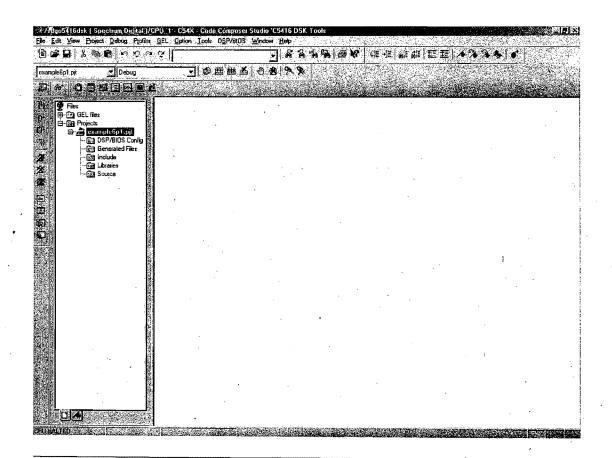

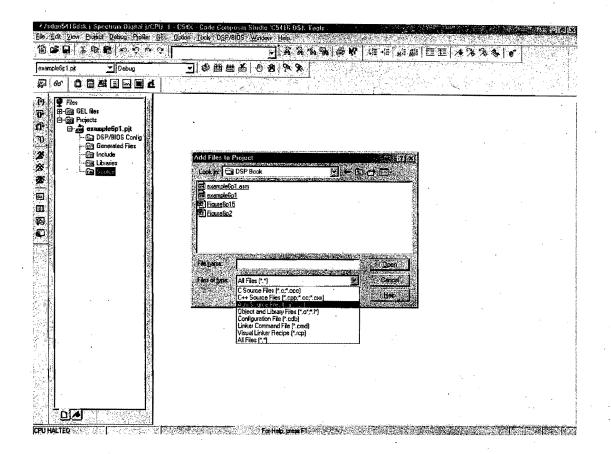

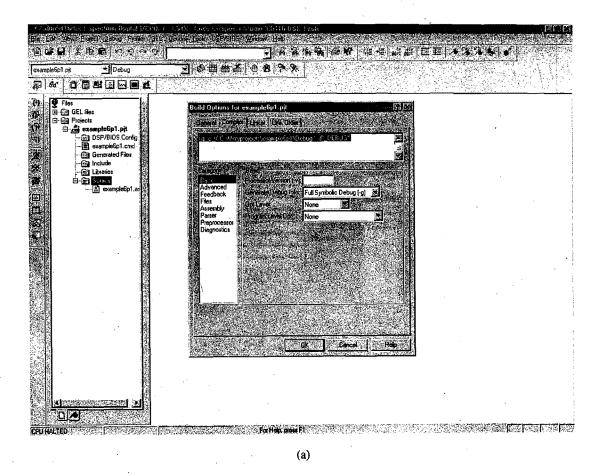

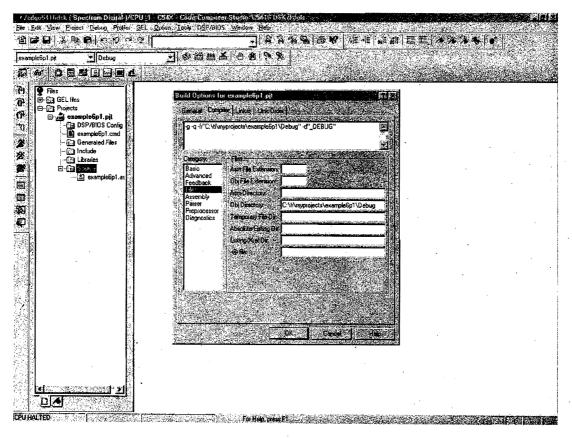

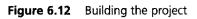

|      | 6.8.1 Building a Project 162     |       |     |     |

|------|----------------------------------|-------|-----|-----|

|      | 6.8.2 The Debug Options 162      | · •   |     |     |

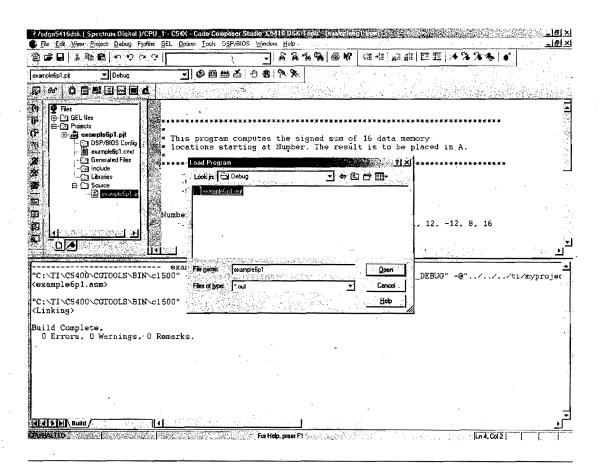

| 6.9  | DSP Software Development Example |       |     | 164 |

| 5.10 | Summary                          |       |     | 167 |

|      | References                       |       |     | 174 |

|      | Laboratory Assignments           | ··· . | • , | 175 |

|      |                                  |       |     |     |

# Chapter 7

| Implementations of Basi       | c DSP Algorit                                                                                                                                                                                                                        | :hms                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        | 176                                                                                                                                                                                                                                    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        | 176                                                                                                                                                                                                                                    |

| The Q-notation                |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        | 176                                                                                                                                                                                                                                    |

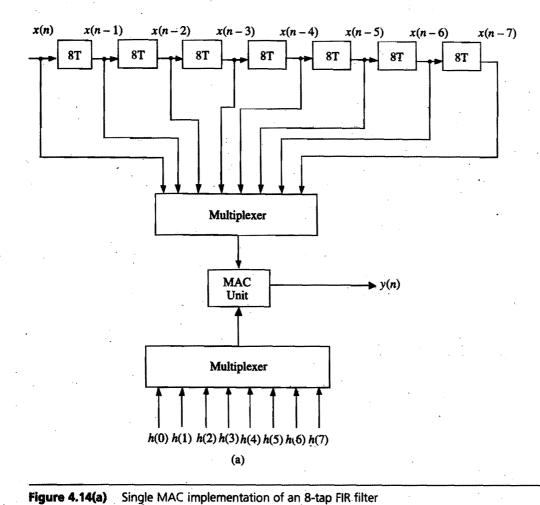

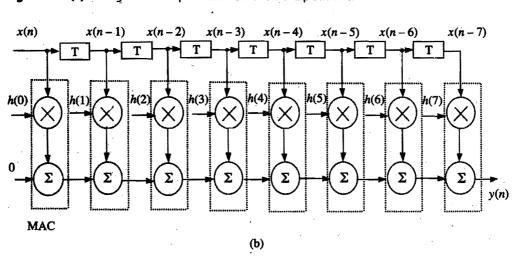

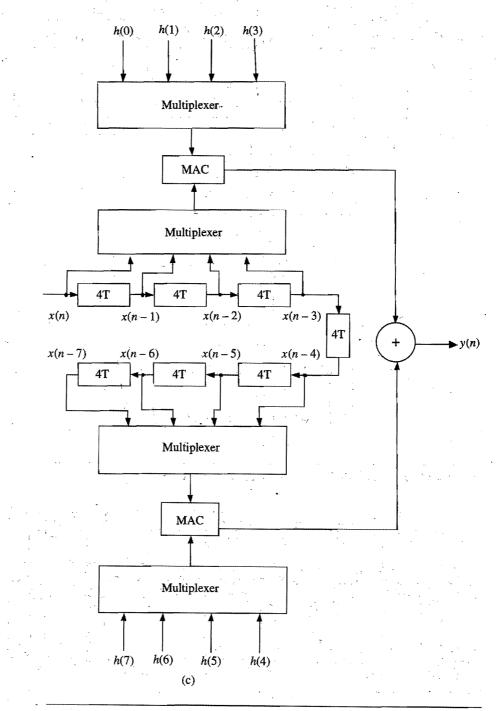

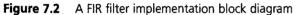

| FIR Filters                   | . `                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        | 178                                                                                                                                                                                                                                    |

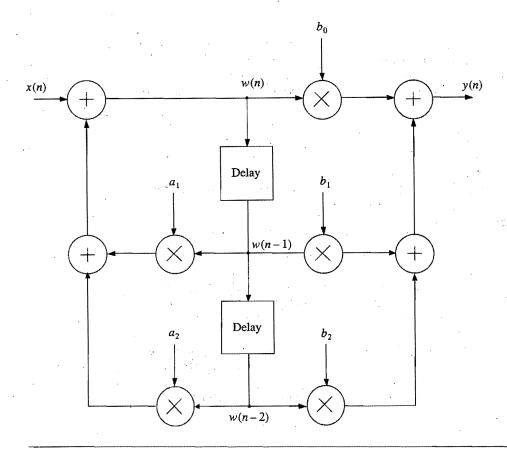

| IIR Filters                   |                                                                                                                                                                                                                                      | •                                                                                                                                                                                                                                      |                                                                                                                                                                                                                        | · 181                                                                                                                                                                                                                                  |

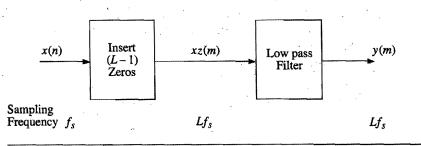

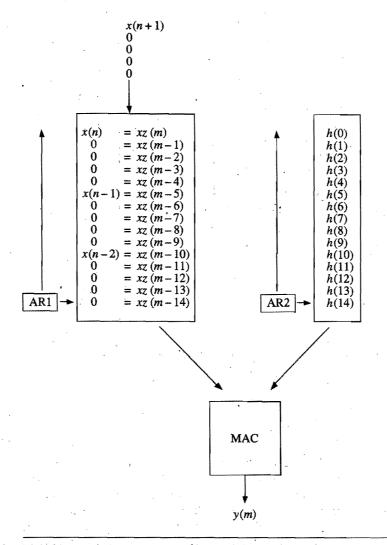

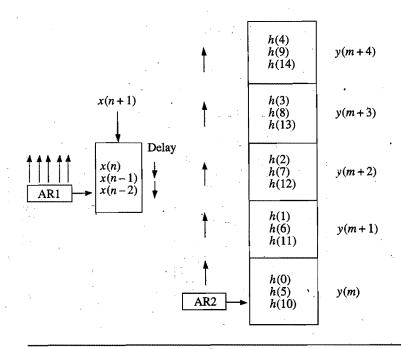

| Interpolation Filters         |                                                                                                                                                                                                                                      | ·                                                                                                                                                                                                                                      |                                                                                                                                                                                                                        | 187                                                                                                                                                                                                                                    |

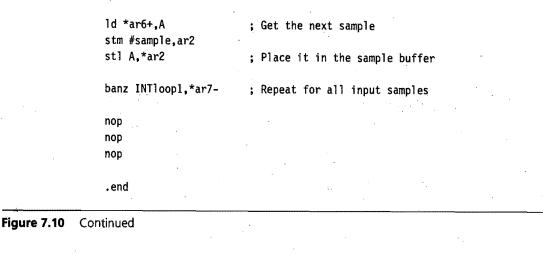

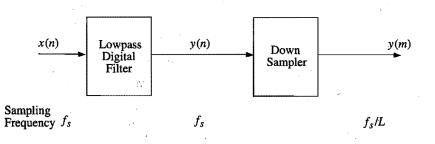

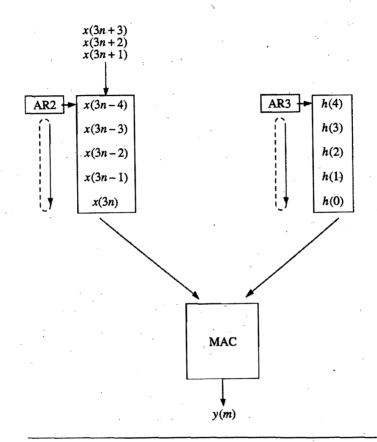

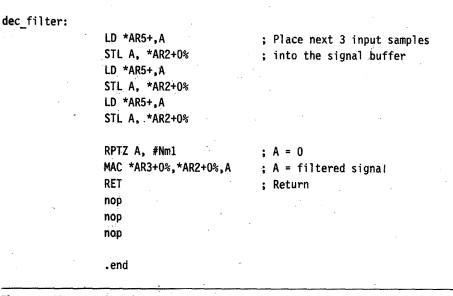

| Decimation Filters            |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        | 190                                                                                                                                                                                                                                    |

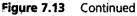

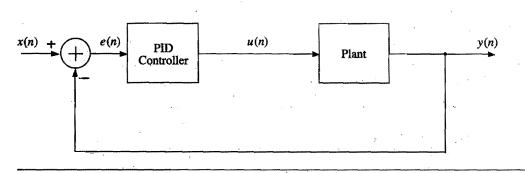

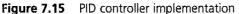

| PID Controller                |                                                                                                                                                                                                                                      | · ·                                                                                                                                                                                                                                    |                                                                                                                                                                                                                        | -193                                                                                                                                                                                                                                   |

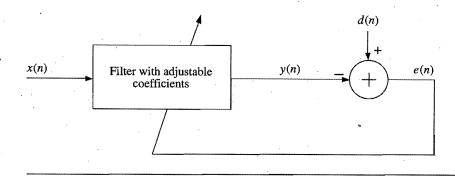

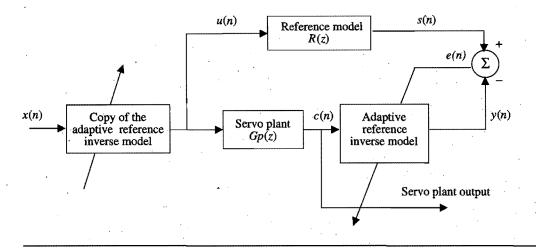

| Adaptive Filters              |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        | 198                                                                                                                                                                                                                                    |

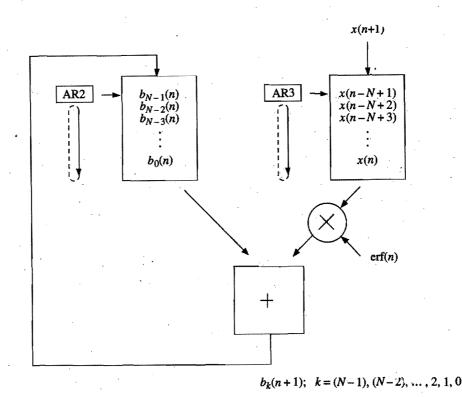

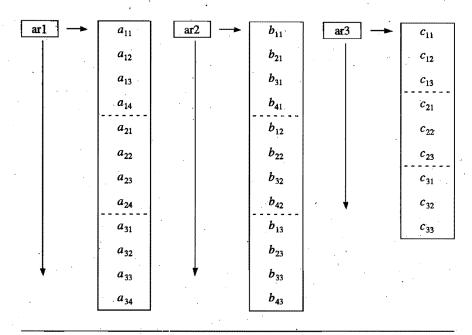

| 2-D Signal Processing         |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        | ·.                                                                                                                                                                                                                     | 201                                                                                                                                                                                                                                    |

| 7.9.1 Matrix Multiplication 2 | 06                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                        | ,                                                                                                                                                                                                                      | ×                                                                                                                                                                                                                                      |

| Summary                       | *                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                        | 4. S. S. S.                                                                                                                                                                                                            | 211                                                                                                                                                                                                                                    |

| References                    |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        | 211                                                                                                                                                                                                                                    |

| Assignments -                 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        | 211                                                                                                                                                                                                                                    |

|                               | Introduction<br>The Q-notation<br>FIR Filters<br>IIR Filters<br>Interpolation Filters<br>Decimation Filters<br>PID Controller<br>Adaptive Filters<br>2-D Signal Processing<br>7.9.1 Matrix Multiplication 2<br>Summary<br>References | Introduction<br>The Q-notation<br>FIR Filters<br>IIR Filters<br>Interpolation Filters<br>Decimation Filters<br>PID Controller<br>Adaptive Filters<br>2-D Signal Processing<br>7.9.1 Matrix Multiplication 206<br>Summary<br>References | The Q-notation<br>FIR Filters<br>IIR Filters<br>Interpolation Filters<br>Decimation Filters<br>PID Controller<br>Adaptive Filters<br>2-D Signal Processing<br>7.9.1 Matrix Multiplication 206<br>Summary<br>References | Introduction<br>The Q-notation<br>FIR Filters<br>IIR Filters<br>Interpolation Filters<br>Decimation Filters<br>PID Controller<br>Adaptive Filters<br>2-D Signal Processing<br>7.9.1 Matrix Multiplication 206<br>Summary<br>References |

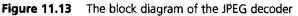

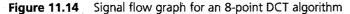

| apter | o<br>Implementation of FFT Algorithms    |                                       | 215 |

|-------|------------------------------------------|---------------------------------------|-----|

| 8.1   | Introduction                             |                                       | 215 |

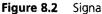

| 8.2   | An FFT Algorithm for DFT Computation     | · · · · · · · · · · · · · · · · · · · | 215 |

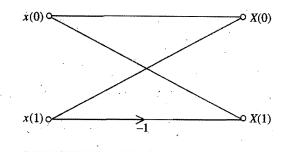

|       | 8.2.1 2-Point DFT Computation 216        |                                       |     |

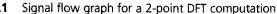

|       | 8.2.2 4-Point DFT Computation 217        |                                       |     |

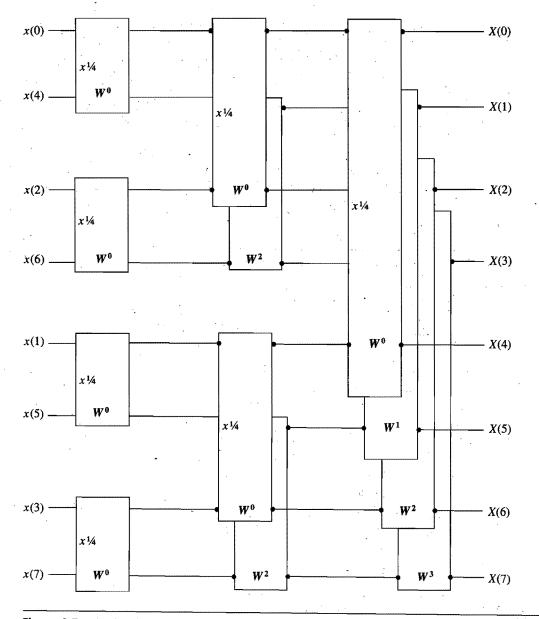

| •     | 8.2.3 8-Point DFT Computation 218        | •                                     |     |

|       | 8.2.4 $N = 2^{M}$ -Point Computation 218 | · · · · · ·                           |     |

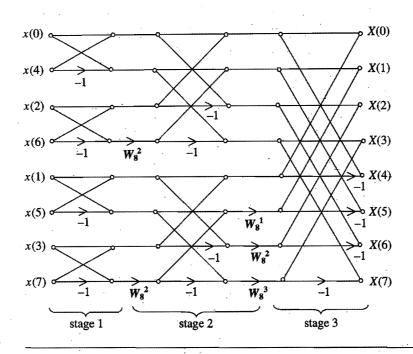

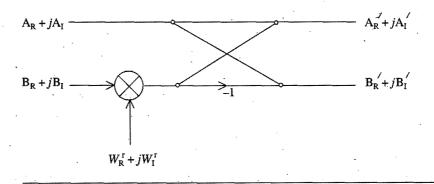

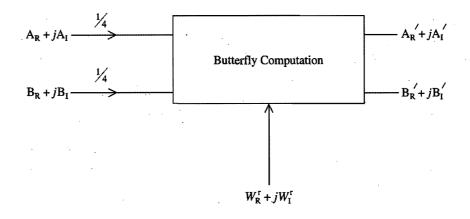

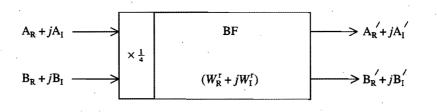

| 8.3   | A Butterfly Computation                  |                                       | 219 |

## viii Contents

| 8.4 | Overflow and Scaling                    |             |    | 220 |

|-----|-----------------------------------------|-------------|----|-----|

| 8.5 | Bit-Reversed Index Generation           | · .         | 2  | 223 |

| 8.6 | An 8-Point FFT Implementation on the TM | //S320C54xx |    | 224 |

| 8.7 | Computation of the Signal Spectrum      |             |    | 232 |

| 8.8 | Summary                                 |             | x. | 233 |

|     | References                              | <u>.</u>    |    | 233 |

|     | Assignments                             | ****        |    | 233 |

|                                                                           | erals to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable DSP Devices                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 236                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Introduction                                                              | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 236                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

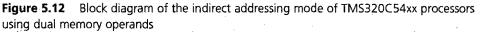

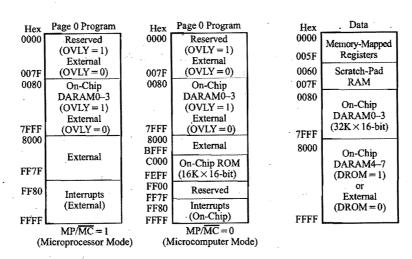

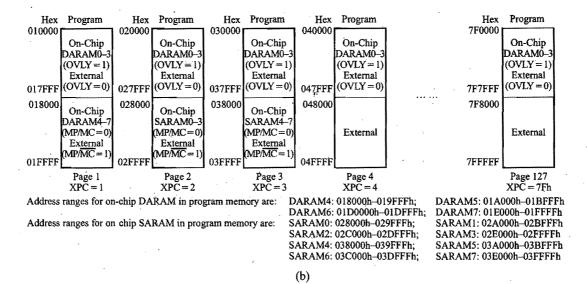

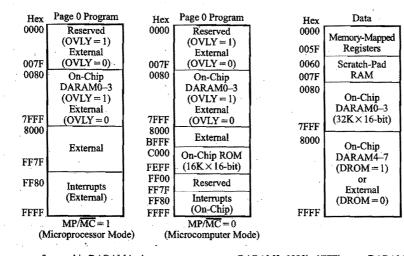

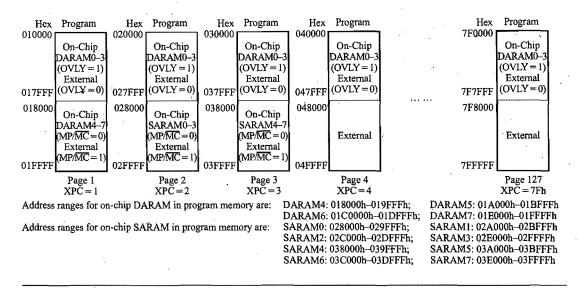

| Memory Space Organization                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 236                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

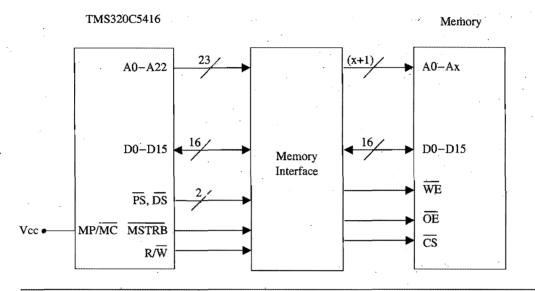

| External Bus Interfacing Signals                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 238                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Memory Interface                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 238                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

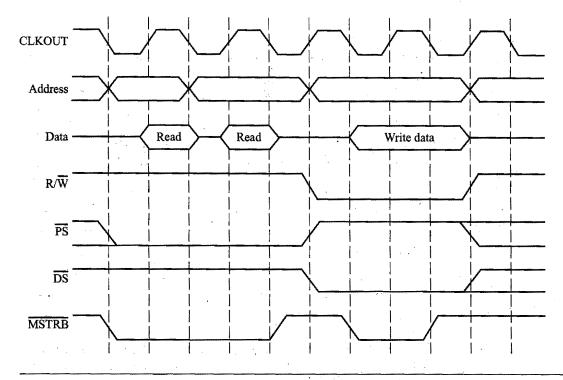

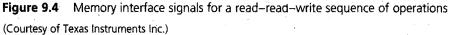

| 9.4.2 Wait States 240                                                     | 239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AC .                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 247                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 248                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| •                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

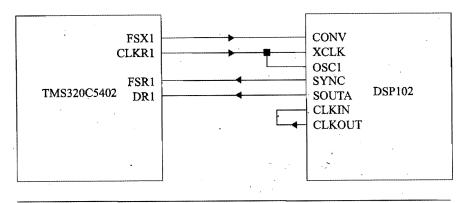

| Direct Memory Access (DMA)                                                | æ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | *<br>*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

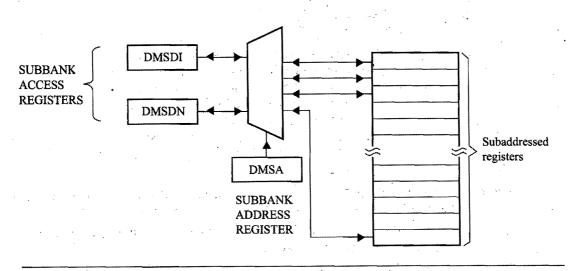

| 9.8.1 DMA Operation Configuration 256<br>9.8.2 Register Subaddressing 257 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Summary                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 259                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| References                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 259                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Assignments                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 260                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Interfacing Serial Converters to a<br>Programmable DSP Device             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 262                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Introduction                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 262                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

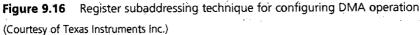

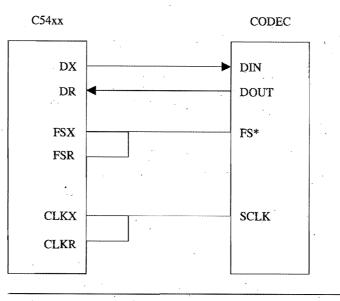

| Synchronous Serial Interface                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 262                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                           | Programmable DSP Devices<br>Introduction<br>Memory Space Organization<br>External Bus Interfacing Signals<br>Memory Interface<br>9.4.1 Timing Sequence for External Memory Access<br>9.4.2 Wait States 240<br>9.4.3 Memory Design Examples 243<br>Parallel I/O Interface<br>Programmed I/O<br>Interrupts and I/O<br>9.7.1 Handling of Interrupts 249<br>Direct Memory Access (DMA)<br>9.8.1 DMA Operation Configuration 256<br>9.8.2 Register Subaddressing 257<br>Summary<br>References<br>Assignments<br><b>10</b><br>Interfacing Serial Converters to a<br>Programmable DSP Device | Introduction<br>Memory Space Organization<br>External Bus Interfacing Signals<br>Memory Interface<br>9.4.1 Timing Sequence for External Memory Access 239<br>9.4.2 Wait States 240<br>9.4.3 Memory Design Examples 243<br>Parallel I/O Interface<br>Programmed I/O<br>Interrupts and I/O<br>9.7.1 Handling of Interrupts 249<br>Direct Memory Access (DMA)<br>9.8.1 DMA Operation Configuration 256<br>9.8.2 Register Subaddressing 257<br>Summary<br>References<br>Assignments<br><b>10</b><br>Interfacing Serial Converters to a<br><b>Programmable DSP Device</b><br>Introduction | Programmable DSP Devices         Introduction         Memory Space Organization         External Bus Interfacing Signals         Memory Interface         9.4.1 Timing Sequence for External Memory Access 239         9.4.2 Wait States 240         9.4.3 Memory Design Examples 243         Parallel I/O Interface         Programmed I/O         Interrupts and I/O         9.7.1 Handling of Interrupts 249         Direct Memory Access (DMA)         9.8.1 DMA Operation Configuration 256         9.8.2 Register Subaddressing 257         Summary         References         Assignments         10         Interfacing Serial Converters to a         Programmable DSP Device         Introduction |

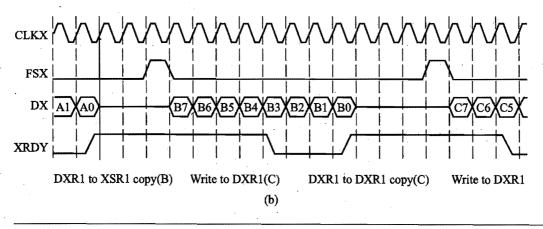

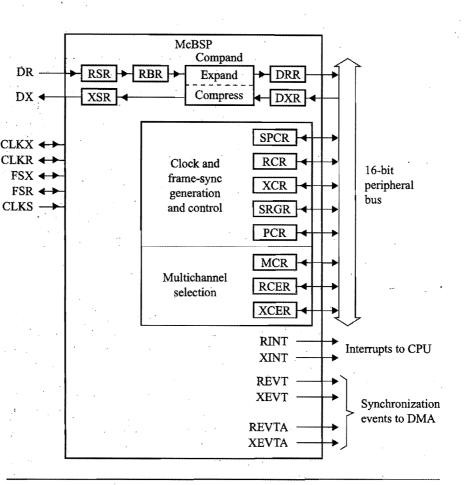

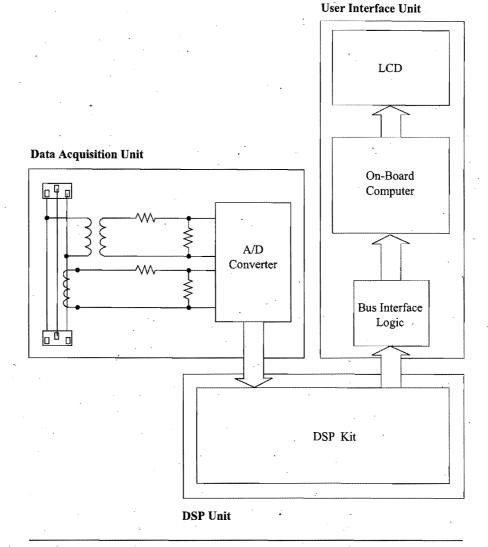

| 10.3 | A Multichannel Buffered Serial Port (McBSP) |             | 264 |

|------|---------------------------------------------|-------------|-----|

| 10.4 | McBSP Programming                           |             | 266 |

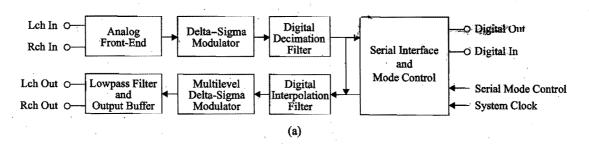

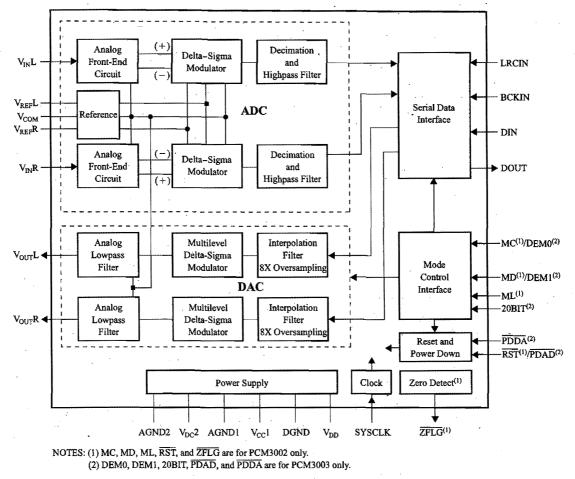

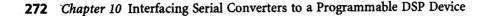

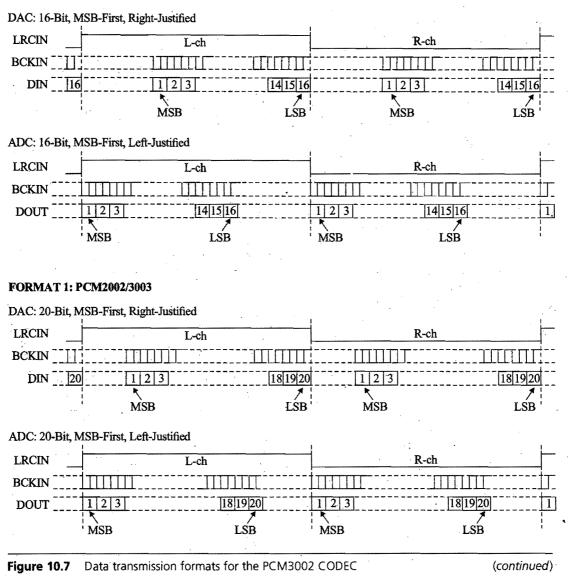

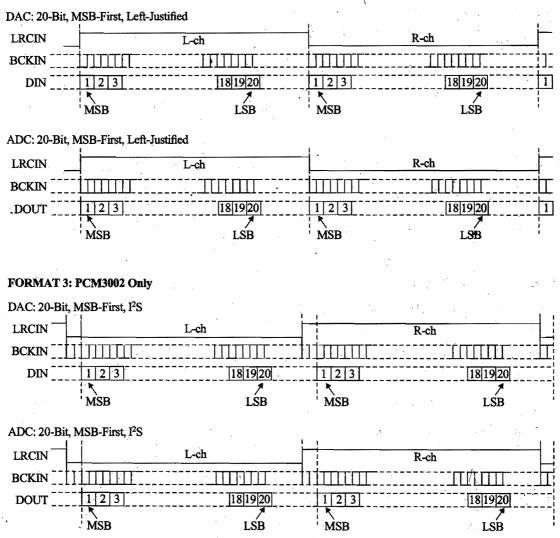

|      | A CODEC Interface Circuit                   | · · · · · · | 266 |

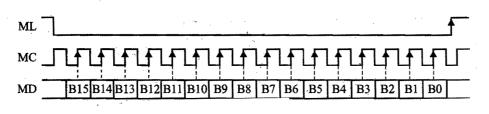

| 10.6 | CODEC Programming                           |             | 275 |

| 10.7 | A CODEC–DSP Interface Example               | ,           | 277 |

| 10.8 | Summary                                     |             | 294 |

|      | References                                  | 424 C 8     | 295 |

|      | Assignments                                 |             | 295 |

|              | Applications of Programmable DSP Devices                                                                                                                                                                          | 297 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>1</b> 1.1 | Introduction                                                                                                                                                                                                      | 297 |

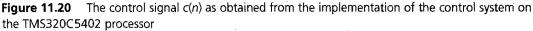

| 11.2         | A DSP System                                                                                                                                                                                                      | 297 |

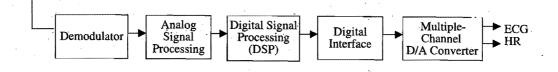

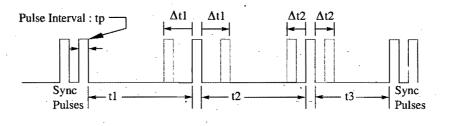

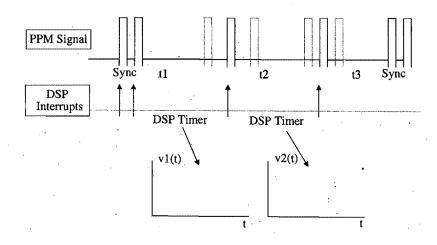

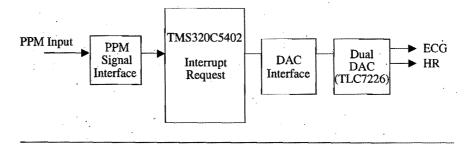

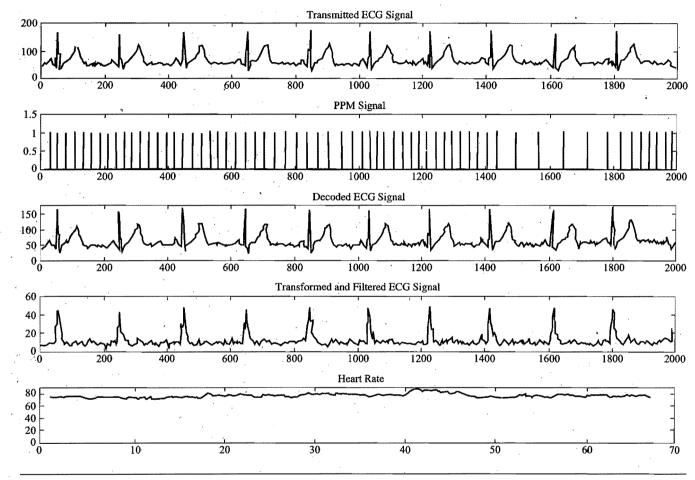

| 11.3         | DSP-Based Biotelemetry Receiver                                                                                                                                                                                   | 298 |

|              | 11.3.1 Pulse Position Modulation (PPM) 299<br>11.3.2 Decoding Scheme for the PPM Receiver 300<br>11.3.3 Biotelemetry Receiver Implementation 301<br>11.3.4 ECG Signal Processing for Heart Rate Determination 301 |     |

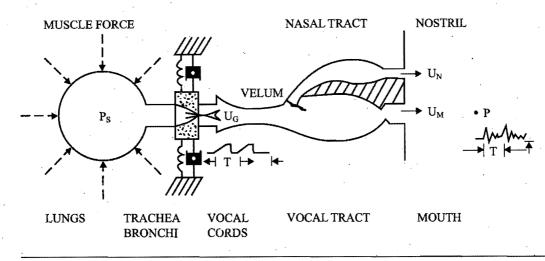

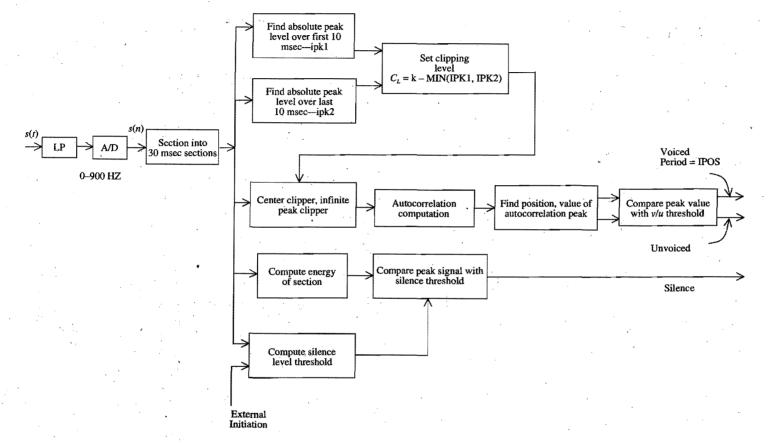

| 11.4         | A Speech Processing System                                                                                                                                                                                        | 302 |

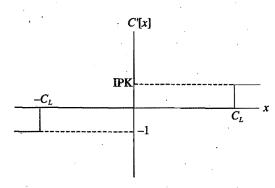

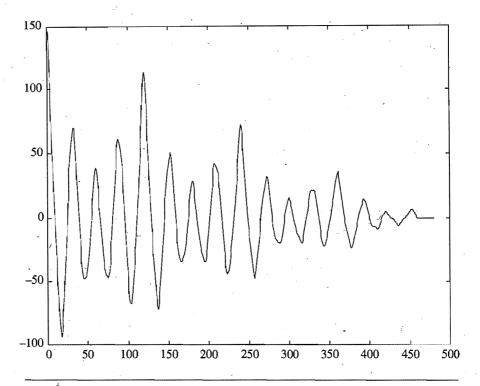

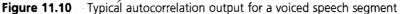

|              | 11.4.1 A Digital Model for Production of Speech Signal 304<br>11.4.2 Autocorrelation 304<br>11.4.3 Implementation on the TMS320C54xx Processor 307                                                                |     |

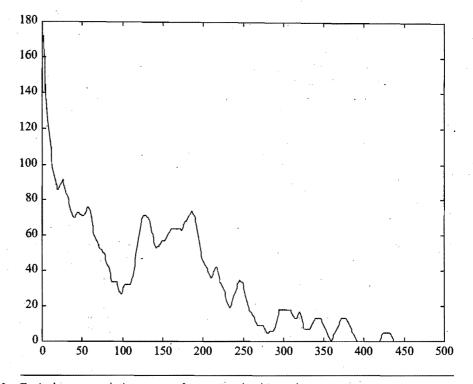

| 11.5         | An Image Processing System                                                                                                                                                                                        | 307 |

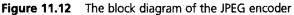

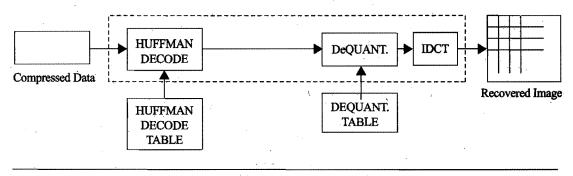

|              | 11.5.1 JPEG Algorithm Overview 309<br>11.5.2 JPEG Encoding 310<br>11.5.3 JPEG Decoding 311<br>11.5.4 Encoding and Decoding of JPEG Using the TMS320C54xx 311                                                      |     |

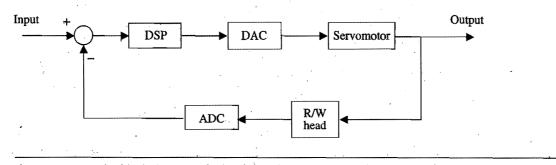

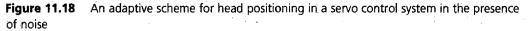

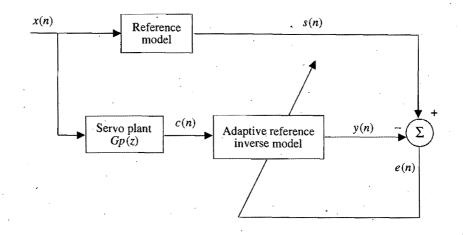

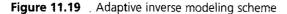

| 11.6         | A Position Control System for a Hard Disk Drive                                                                                                                                                                   | 312 |

| 11.7         | DSP-Based Power Meter                                                                                                                                                                                             | 316 |

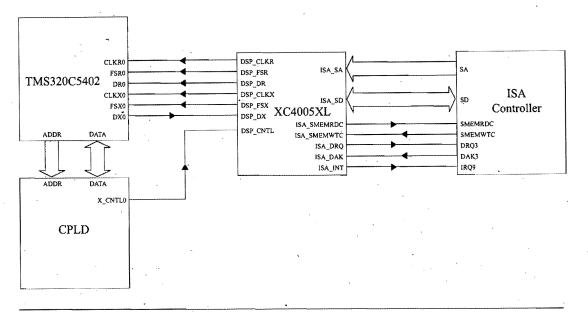

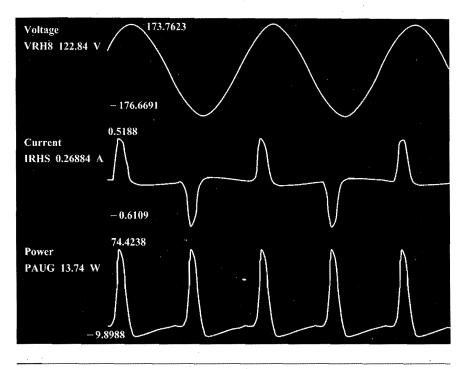

|              | 11.7.1 Power Measurement System 317<br>11.7.2 Software for the Power Meter 320                                                                                                                                    |     |

| 11.8         | Summary                                                                                                                                                                                                           | 322 |

|              | References                                                                                                                                                                                                        | 322 |

|              |                                                                                                                                                                                                                   |     |

**x** Contents

# Appendix ${f A}$

## Architectural Details of TMS320VC5416 Digital Signal Processor

Index

339

323

# Preface

Due to advances in VLSI technology, programmable DSP devices are becoming increasingly available and affordable. These devices have, therefore, become popular in the industry for the design of products. Consequently, a large number of undergraduate senior projects and graduate projects are planned and implemented using these devices. Many students attempt these projects based on a first-level course on digital signal processing. The books that are used in these classes do not, however, cover the topics from the implementation point of view. There is generally a wide gap in students' understanding of DSP algorithms and how to use programmable DSP devices to implement them.

This is a DSP implementation-oriented textbook that has been written based on the authors' experience in teaching graduate and undergraduate courses on the subject. The objective of the book is to help the reader to understand the architecture, programming, and interfacing of commercially available programmable DSP devices and to effectively use them in system implementations. The book is intended for senior undergraduate and firstlevel graduate students in electrical engineering and computer science programs. The book will also be useful to engineers in industry engaged in the design of DSP systems. The background expected from a reader is a course in digital signal processing and a course in microprocessors, both at the undergraduate level.

This book contains 11 chapters and covers the architectural issues of programmable DSP devices and their relationship to the algorithmic requirements, architectures of commercially popular programmable devices, and the use of such devices for software development and system design. These issues are covered using a popular family of DSP devices—TMS320C54xx from Texas Instruments.

Chapter 1 identifies the role of programmable devices in the implementation of DSP-based systems. Chapter 2 reviews the DSP basics so that the reader can correlate the remainder of the book to the theoretical requirements of a DSP system. The aim is not to attempt to teach DSP theory, which is abundantly covered elsewhere, but to highlight the concepts that are relevant from the point of view of implementations. MATLAB is used as a tool in exploring and understanding the basic DSP concepts. Chapter 3 looks at issues that determine the computational accuracy of algorithms when implemented using programmable DSP devices. Although it is desirable to retain as much accuracy as possible when DSP algorithms are implemented in hardware, in a practical implementation, accuracy has to be measured against the speed of operation and hardware complexity. Different number representation schemes are introduced and their effects on precision and dynamic range are discussed. Various sources of errors in a DSP system are described and are quantitatively evaluated in this chapter.

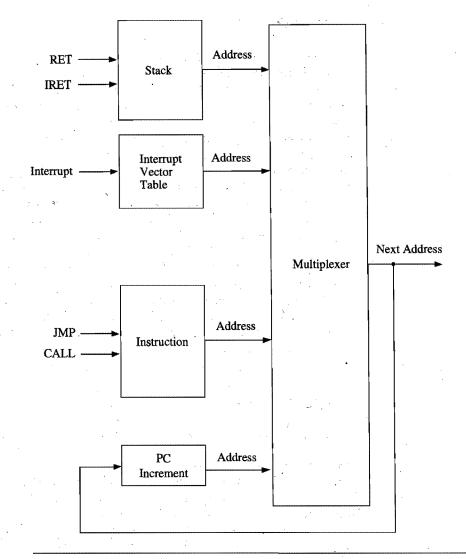

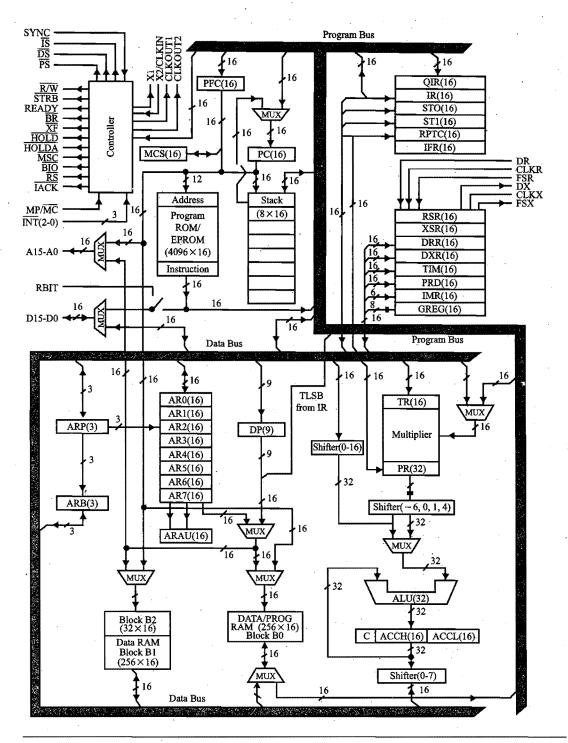

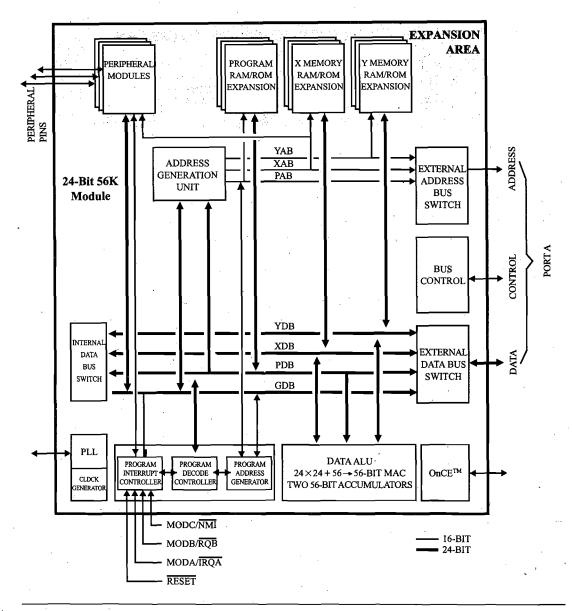

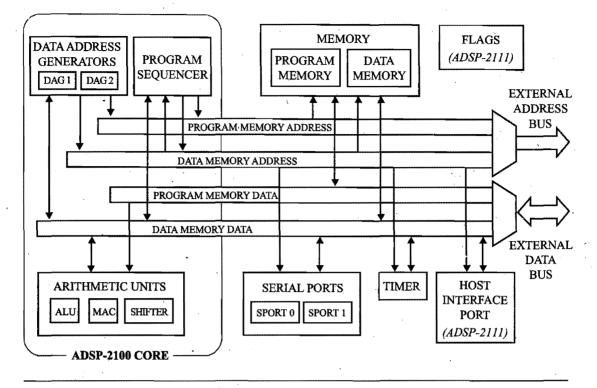

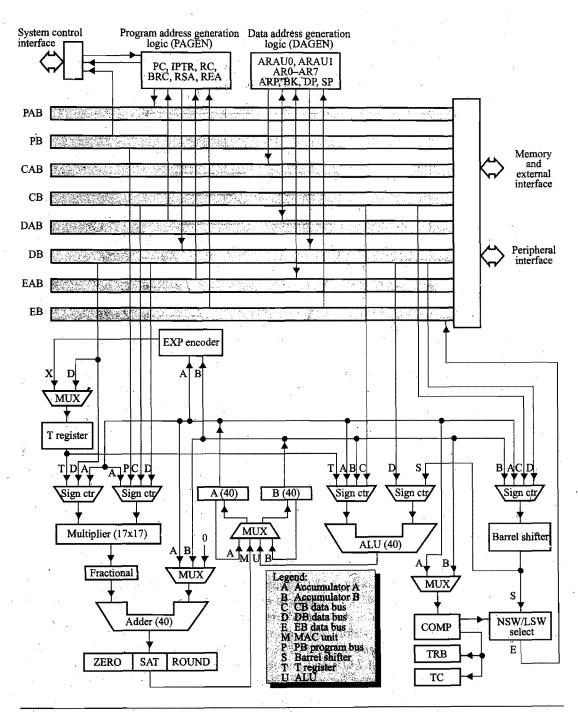

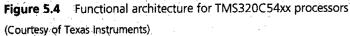

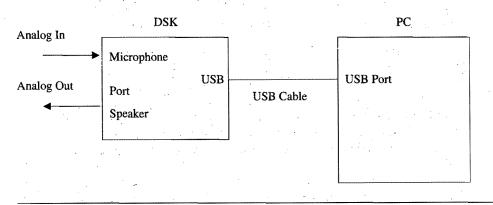

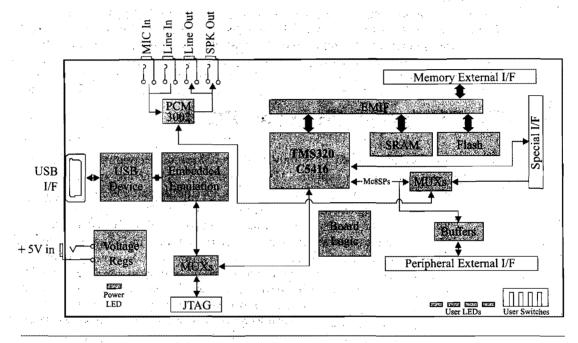

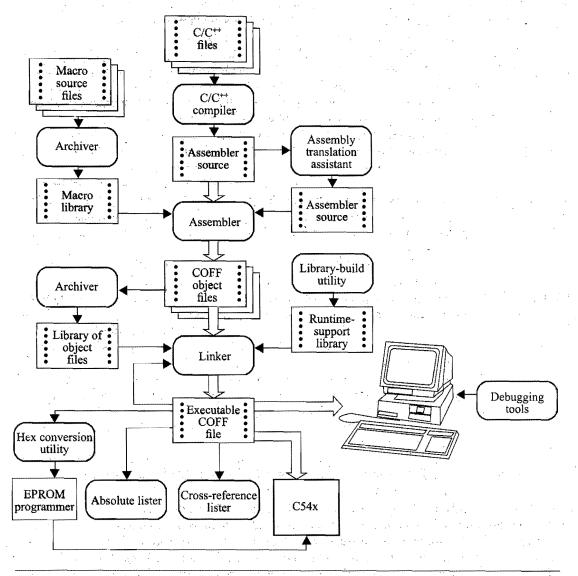

One of the objectives of the book is to give readers sufficient exposure to the architecture of programmable DSP devices so that they can use them effectively and optimally in designing systems. Chapter 4 explains the architectural features of programmable DSP devices based on the operations these devices are required to perform. Various building blocks that constitute a programmable digital signal processor are discussed from the point of view of implementations. Desirable features for each of these blocks are discussed in terms of their hardware realization. Chapter 5 introduces the Texas Instruments' TMS320C54xx family of fixed-point DSP processors and discusses their architecture, software, and hardware features. These devices are used in programming and design examples throughout the book. Chapter 6 introduces the various tools that are available for the development of DSP software on programmable devices. In particular, the use of DSK5416, a system design kit used for program development for the TMS320C54xx, and the development software called Code Composer Studio are described. The DSK5416 is the development board around which all the designs are implemented in subsequent chapters.